## On Improving Dependability of Analog and Mixed-Signal SoCs: A System-Level Approach

Muhammad Aamir Khan

#### Members of the dissertation committee:

| Prof. dr. ir. | G.J.M Smit       | University of Twente (promoter)               |

|---------------|------------------|-----------------------------------------------|

| Dr. ir.       | H.G. Kerkhoff    | University of Twente (co-promoter)            |

| Prof. dr. ir. | A. Pras          | University of Twente                          |

| Prof. dr. ir. | A.J.M. van Tuijl | University of Twente                          |

| Prof. dr.     | J. Figureras     | Universitat Politècnica de Catalunya (Spain)  |

| Prof. dr.     | A. Richardson    | Lancaster University (United Kingdom)         |

| Dr. ir.       | S. Hamdioui      | Delft University of Technology                |

| Prof. dr.     | P. Apers         | University of Twente (chairman and secretary) |

This work has been carried out as part of the Catrene project "TOETS" [CT302] and supported by the Netherlands Enterprise Agency.

CTIT Ph.D. Thesis Series No. 14-328 Center for Telematics and Information Technology University of Twente, P.O. Box 217, NL-7500 AE Enschede, The Netherlands.

Copyright © 2014 by Muhammad Aamir Khan, Enschede, The Netherlands. Cover designed by Muhammad Aamir Khan.

All rights reserved. No part of this book may be reproduced or transmitted, in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage or retrieval system, without prior written permission of the author.

Typeset with Microsoft Word 2010. This thesis was printed by Gilderprint Drukkerijen, the Netherlands.

ISBN 978-90-365-3777-3

ISSN 1381-3617 (CTIT Ph.D. Thesis Series No. 14-328)

DOI 10.3990./1.9789036537773

## ON IMPROVING DEPENDABILITY OF ANALOG AND MIXED-SIGNAL SOCS: A SYSTEM-LEVEL APPROACH

#### DISSERTATION

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof. dr. H. Brinksma,

on account of the decision of the graduation committee

to be publicly defended

on Friday, 7<sup>th</sup> of November 2014 at 16.45

by

Muhammad Aamir Khan

born on 25<sup>th</sup> of June 1979, in Mianwali, Pakistan

#### This dissertation is approved by:

Prof. dr. ir. G.J.M Smit University of Twente (promoter)

Dr. ir. H.G. Kerkhoff University of Twente (co-promoter)

#### **ABSTRACT**

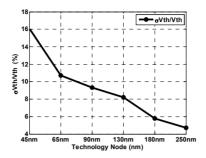

Dependability of electronic systems, being an indispensable part of our civilian, industrial and military applications, has become increasingly important as a result of continuous technology scaling. The dependability or human reliance on these electronic systems has decreased as a result of new technologies which are far less mature as compared to older technologies. The electrical characteristics of the transistors and the wires will vary statistically in a spatial and temporal manner, directly translating into design uncertainty during fabrication and even during operational life. This combined impact of manufacturing uncertainty (e.g. process variability) and temporal degradation (aging) results in time-dependent variability and hence the means to impact the functionality and dependability of electronic systems.

Unfortunately, traditional worst-case design slacks or margins are not sufficient anymore to capture the time-dependent system variability, especially in new technology nodes, and would result in over-pessimistic implementations with significant penalties in terms of area/delay/energy. As a result, time-dependent uncertainties become a great threat to the design of complex systems-on-chip (SoC) implementations and their dependability. It becomes extremely important in case of safety- or mission-critical systems because the dependability failure of these systems may result in enormous cost damage or even loss of human lives. Therefore, maintaining or achieving high system dependability in safety- or mission-critical systems is the most important property.

Analog and mixed-signal front/back ends, being an important part of most critical systems especially in safety-critical (e.g. automotive, medical etc.) and mission-critical (e.g. military, space etc.) systems have received relatively little attention with regard to dependability. The dependability of these analog and mixed-signal front/back ends is essential in order to have a dependable interface between the real world and digital world. This is the main goal of the current research where new system-level strategies have been explored and investigated in order to enhance the dependability of analog and mixed-signal front ends especially during their operational life.

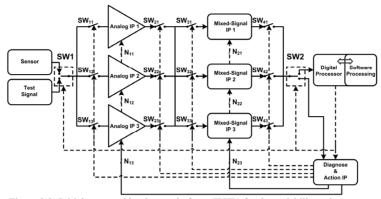

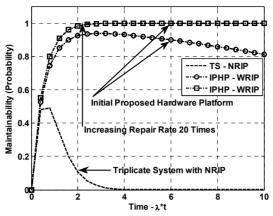

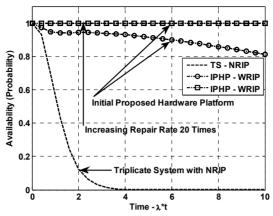

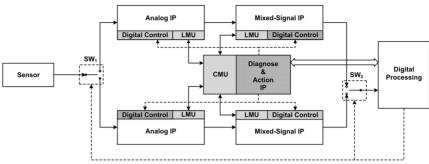

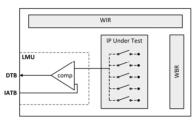

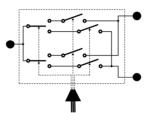

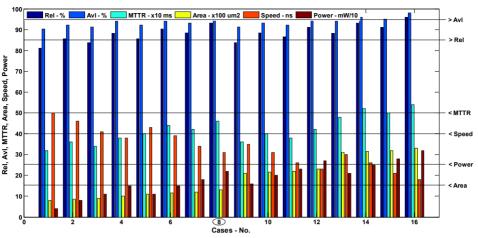

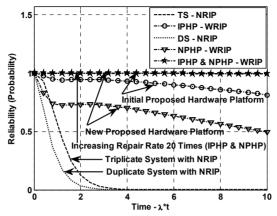

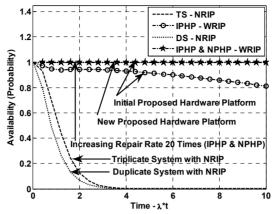

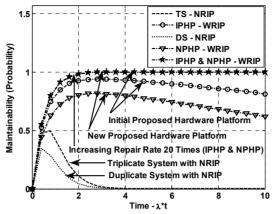

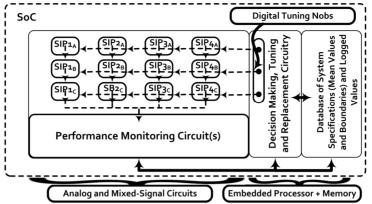

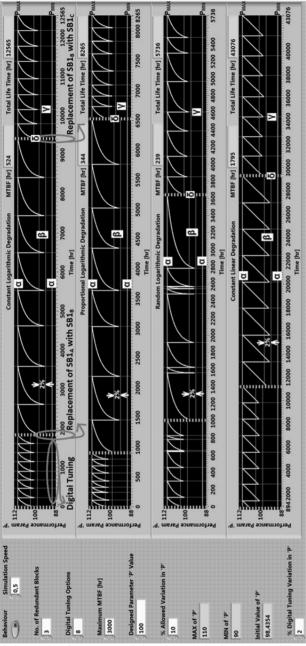

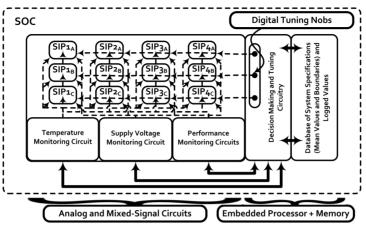

A system-level hardware platform has been proposed as a potential solution to enhance the dependability of analog and mixed-signal front ends. The idea is to diagnose the performance of analog and mixed-signal front ends at regular intervals of time and in case of performance deviations from the designed specifications take the necessary repair actions. The proposed hardware platform is based on digitally-assisted redundant/spare hardware units concept where a separate hardware block is responsible for taking performance measurements and the corresponding repairing actions via built-in digital tuning capabilities or using a switch matrix to replace the faulty hardware units with the fault-free spare hardware units. The theoretical/mathematical dependability evaluation of the proposed hardware platform shows dependability improvements at the cost of extra hardware. However, a new hardware platform is proposed that can achieve similar results of dependability with reduced area overhead. Further improvements in area, speed and power requirements along with different values of dependability are optimized using the concept of library of dependable IPs;

vii

proposed in this research work. The idea is to use the design-stage simulation results to construct a library of dependable IPs with a number of IPs having the same functionalities but different values of dependability along with their speed, area, and power overheads. This library can be further used in selecting the best combination of IPs resulting in an optimization between the required dependability and the associated penalties in terms of area, speed and power. This library of dependable IPs, coupled with the new hardware platform, is used to achieve higher dependability in analog and mixed-signal front ends.

viii

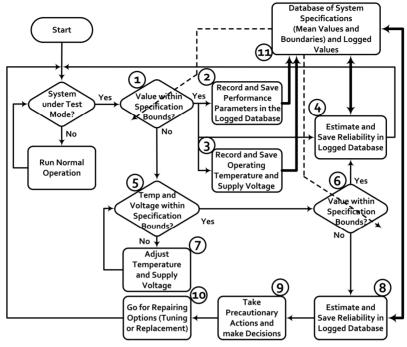

The above proposed hardware platform resolves the time-dependent degradation issues in analog and mixed-signal front ends during their operational life. However, it has been observed that the initial variations as a result of fabrication-related process variations have a significant effect on the degradation behavior of similar systems. Some systems will degrade more quickly as compared to other similar systems. This issue has been resolved by introducing a database of system specifications and runtime logged measurements of the system performance parameters to exactly know the degradation behavior of a system and to know more precisely at what point in time the repair actions have to be taken in order to avoid dependability failures. Furthermore, in order to avoid the potential circuit over loading effects while directly interacting with the system internal nodes for performance measurements, an indirect novel technique to estimate the system performance during its operational life is also presented. The indirect technique, in combination with the database of system specifications and logged values of system performance measurements, is further used to effectively achieve higher dependability in analog and mixed-signal front ends.

The time-dependent and process-induced initial-value dependent degradation effects are further related to the working stress conditions and the corresponding duration of stress time. Among them are the working stress temperature and working stress voltage. These stressors can be differentiated as short-term and long-term based on the duration of time these stressors are applied. This will further lead to short-term variations (or temporary) and long-term variations (could be permanent). These short-term and long-term variations need to be differentiated in order to efficiently enhance the dependability of analog and mixed-signal front ends. This concept has been incorporated in the proposed strategy where a continuous monitoring of the working stress temperature and working stress voltage has been performed in order to take the necessary actions in maintaining these stressors within their specifications and for selecting the appropriate repair strategies in order to further enhance the dependability of the analog and mixed-signal front ends.

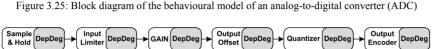

As an example of a relatively complex system and an essential part of analog and mixed-signal front ends, the charge-redistribution successive approximation register (SAR) ADC has been considered to analyze the time-dependent degradation issues in its static and dynamic performance parameters. Usually, transistor-level aging simulations are very time consuming for these types of systems. Therefore, behavioral models, that have been frequently used to analyze the performance of electronic systems, are used to simulate the degradation effects in a SAR ADC. The SAR ADC has been subdivided into smaller sub-blocks and the degradation information of each sub-block has been incorporated in their respective behavioral models to simulate the degradation effects in the complete SAR ADC. A flexible simulation setup has been constructed in the

LabVIEW environment where different important parameters of the SAR ADC can be selected to see the corresponding degradation effects in its static and dynamic performance parameters. This degradation information has been further used in proposing system-level strategies to enhance the dependability of SAR ADCs during their operational life.

ix

#### **ACKNOWLEDGEMENTS**

This dissertation is not only a result of the continuous hard work, enthusiasm, perseverance, and consistence efforts during the past four years, but also the encouragement, cooperation, and support from a number of people. Therefore, I would like to take this opportunity to pay my sincere thanks to all of them.

First of all, I would like to express my special gratitude to my supervisor Dr. ir. Hans G. Kerkhoff, who has remained a tremendous mentor throughout my research work. His continuous scientific nourishments and encouraging attitude gave me the confidence to grow as an independent scientific researcher. He taught me the art of critically analyzing the scientific issues, the scientific skills to think for novel solutions, and the effective methodology of technical writing and presentation. His cooperation, open-minded attitude, long scientific discussions, and open-door policy has helped me very substantially in completing the research and obtaining meaningful results. His advice on both research as well as on my career have been priceless. His relentless determination and dedication to scientific research, sincerity and devotion towards his scientific duties, and the thrill to attain perfection will always remain a source of inspiration and guidance to me.

I would also like to pay my special thanks to my promoter Prof.dr.ir. G.J.M. Smit for his continuous support, encouragement, and devoting his precious time in reviewing my thesis. Moreover, I would like to thank all the members of dissertation committee for their valuable comments and participation in the public defense of this dissertation.

Furthermore, I would like to thank my research colleague Jinbo Wan for his valuable support during all scientific discussions and providing me the Cadence simulation environment to run aging simulations. I would also like to thank all of my former and current office colleagues: Vincent Kerzerho, Alireza Rohani, Ahmed Ibrahim, Andreina Zambrano, Yong Zhao, Xiao Zhang, Xiaoqin Sheng, Philip Hölzenspies, Berend Dekens, and Koen Blom for valuable suggestions, help and making my stay enjoyable. Also special thanks to Bert Helthuis for providing all sorts of technical assistance and to Marlous Weghorst, Nicole Baveld, and Thelma Nordholt for their supporting role in all administrative matters during my stay. I would also like to thank all of my Pakistani friends and families with whom we arranged different cultural, social, and sport events. It has been a source of tremendous pleasure and enjoyment to spend time with them.

In the end, I would like to pay my deepest thanks to my family. My beloved mother, who is not in this world anymore but her love, affection and encouragements will always remain with me throughout my life. I can not express my gratitude for her in words, she had always prayed for my success and her lovely memories will remain my greatest strength. My cherished father, who has always guided and encouraged me in every aspect of life and his constant inspiration and support kept me focused and motivated throughout my studies. It is only because of his prayers that I sustained thus far. I also sincerely acknowledge my brother, his smiling and advocating attitude also kept me devoted to my research work. I am especially thankful to my wife for her

patience and caring attitude during my studies. I extend my wholehearted thanks for her love, respect and support.

Finally, my greatest regards to the Almighty Allah for bestowing upon me the courage to face the complexities of life and completing this research successfully.

Muhammad Aamir Khan Enschede, November 2014

## **CONTENTS**

| Abstra | ct      |                                                         | vii  |

|--------|---------|---------------------------------------------------------|------|

| Ackno  | wledgen | ients                                                   | xi   |

| Conte  | nts     |                                                         | xiii |

| 1      | Intro   | duction                                                 | 1    |

|        | 1.1     | Dependability and its Importance                        |      |

|        | 1.2     | Dependability Issues In Advanced Technology Nodes       |      |

|        | 1.3     | Dependability Issues in Analog and Mixed-Signal Systems |      |

|        | 1.4     | Traditional Dependability Improvement Pitfalls          |      |

|        | 1.5     | Problem Statement and Research Questions                |      |

|        | 1.6     | Presented Approach                                      |      |

|        | 1.7     | Thesis Organization                                     |      |

|        | 1.8     | References                                              | 7    |

| 2      | Rack    | ground and Related Work                                 | 9    |

|        | 2.1     | Introduction                                            |      |

|        | 2.2     | Dependability                                           |      |

| •      | 2.2.1   | Dependability Attributes                                |      |

|        | 2.2.2   | Dependability Impairments                               |      |

|        | 2.2.3   | Dependability Means                                     |      |

| 2      | 2.3     | Selected Dependability Attributes                       |      |

| 2      | 2.4     | Dependability Theory                                    |      |

|        | 2.4.1   | Reliability Theory                                      |      |

|        | 2.4.2   | Maintainability Theory                                  | 14   |

|        | 2.4.3   | Availability Theory                                     | 15   |

| 2      | 2.5     | Degradation Mechanisms and System Dependability         | 15   |

|        | 2.5.1   | Bias Temperature Instability                            | 16   |

|        | 2.5.2   | Hot Carrier Injection                                   | 16   |

|        | 2.5.3   | Time-Dependent Dielectric Breakdown                     | 17   |

|        | 2.5.4   | Electro-migration                                       | 17   |

| 2      | 2.6     | Analog and Mixed Signal Dependability Improvements      | 17   |

|        | 2.6.1   | Brief History                                           | 17   |

|        | 2.6.2   | Recent Practices                                        | 18   |

|        | 2.6     | 5.2.1 Device-Level Efforts                              | 18   |

|        | 2.6     | 5.2.2 Design-Level Efforts                              | 18   |

|        | 2.6     | 5.2.3 Simulation-Tool Level Efforts                     | 19   |

Degradation Analysis Examples 20

Degradation Mitigation Examples 20

Considerations in the Current Research 22

Working Principle 49

Modelling Analog and Mixed-Signal Front-End.......55

2.6.2.4

2.6.2.5

3.7.1.3

3.9.3.1

3.9.4.1

3.9.4.2

3 10 1 1

3.8

3.9

3.9.1

3.9.2 3.9.3

3.9.4

3.10.1

3.10

2.6.3 2.6.4

|         | A. Modelling a Temperature Sensor                                 |     |

|---------|-------------------------------------------------------------------|-----|

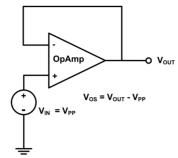

|         | B. Modelling an Operational Amplifier                             | 56  |

|         | A. Modelling the Analog-to-Digital Converter                      | 56  |

| 3.10.2  | 2 Simulation Setup                                                | 57  |

| 3.1     | 10.2.1 Simulation Results                                         | 57  |

| 3.11    | Conclusions                                                       | 60  |

| 3.12    | References                                                        | 60  |

| 4 Run   | time Reliability Estimations and System Dependability             | 63  |

| 4.1     | Introduction                                                      | 63  |

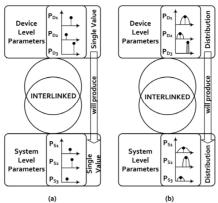

| 4.2     | Hierarchical Flow of System Specifications                        | 65  |

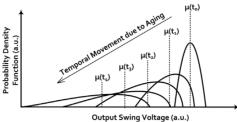

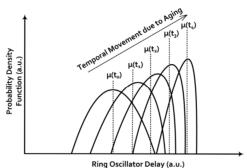

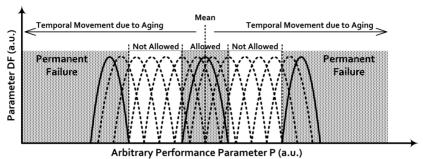

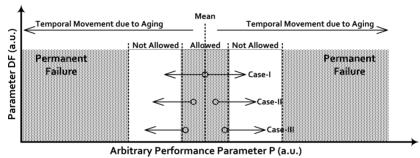

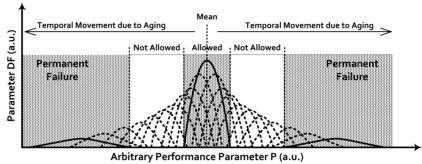

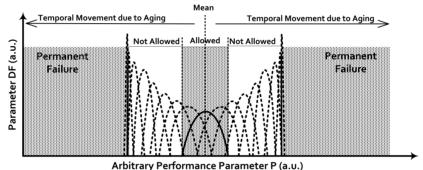

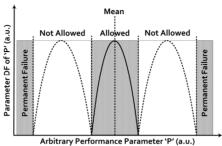

| 4.3     | Variations in System-Level Parameters                             | 66  |

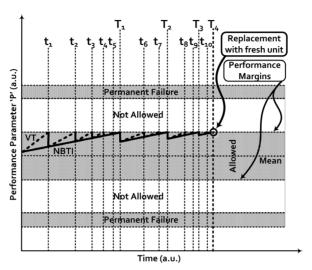

| 4.3.1   | Parameter Variations vs Temporal Degradations                     | 69  |

| 4.4     | Runtime Reliability Requirements                                  | 70  |

| 4.5     | Critical Performance Parameters                                   | 73  |

| 4.6     | Quantitative Runtime Reliability Estimation                       | 74  |

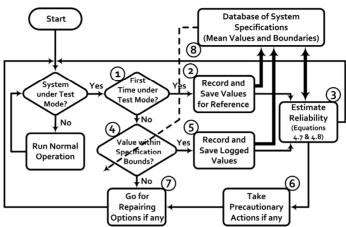

| 4.7     | Proposed Dependability Workflow                                   | 76  |

| 4.7.1   | Working Principle                                                 | 76  |

| 4.7.2   | Dependability Improvements                                        | 78  |

| 4.8     | Simulations and Results                                           | 78  |

| 4.8.1   | Simulation Setup                                                  | 79  |

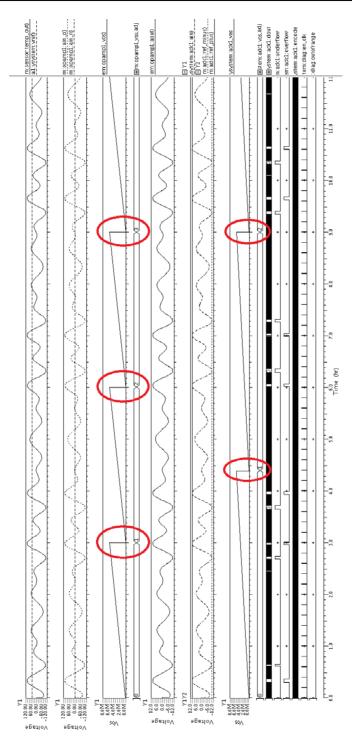

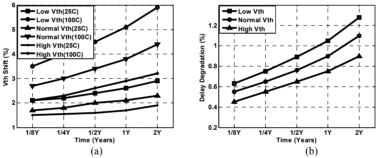

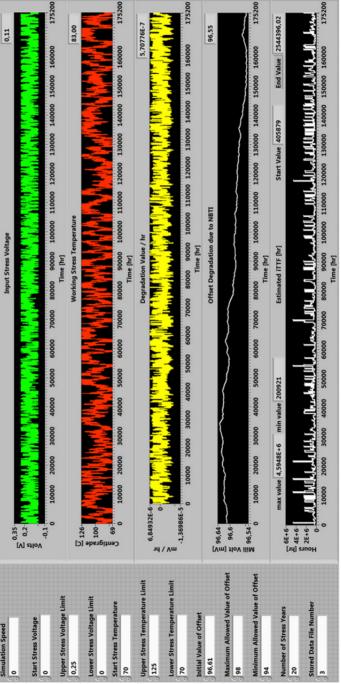

| 4.8.2   | Simulation of Degradation Behaviours                              | 80  |

| 4.8.3   | The Simulator GUI                                                 | 80  |

| 4.8.4   | Randomly Selected Values                                          | 82  |

| 4.8.5   | The Simulation Results                                            | 83  |

| 4.8.6   | Possible Overhead and Overall Performance                         | 85  |

| 4.9     | Indirect Reliability Estimation                                   | 85  |

| 4.9.1   | Design-Stage Degradation Rate Extraction                          | 86  |

| 4.9.2   | Indirect Reliability Estimation Approach                          | 89  |

| 4.9     | 9.2.1 Calculations for an Example Target System                   | 90  |

| 4.9     | 9.2.2 Simulation Setup                                            | 93  |

| 4.9     | 9.2.3 Simulation Results                                          | 94  |

| 4.10    | Conclusions                                                       | 99  |

| 4.11    | References                                                        | 99  |

| 5 Diffe | erentiating Between Short-Term and Long-Term Dependability Issues | 103 |

| 5.1     | Introduction                                                      |     |

| 5.2     | Supply-Voltage and Temperature Variations                         | 104 |

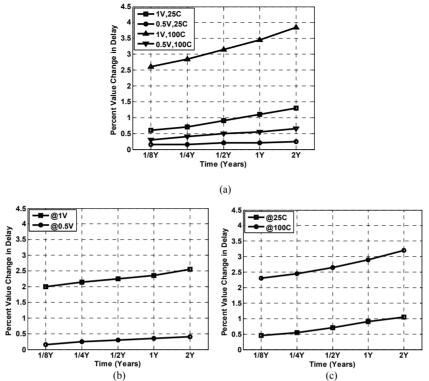

| 5.2.1   | Supply-Voltage and Temperature Variations in Digital Systems      | 105 |

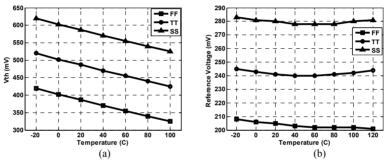

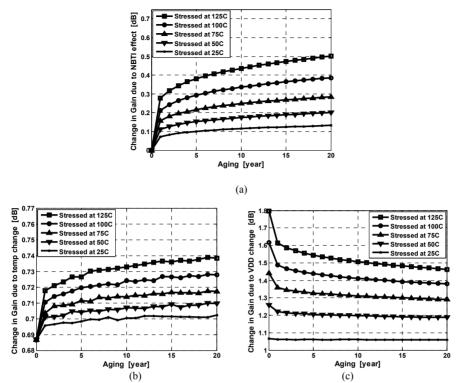

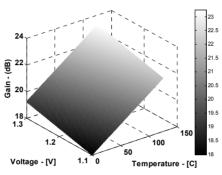

| 5.2.2   | Supply-Voltage and Temperature Variations in Analog Systems       | 106 |

| 5.2.3   | The Role of Supply-Voltage and Temperature Variation              | 108 |

|     | 5.3 The Importance of Separating NBTI and Supply-Voltage and Temperatur<br>108 |                                                                   | √ariations |

|-----|--------------------------------------------------------------------------------|-------------------------------------------------------------------|------------|

|     | 5.4                                                                            | Enhancing the System Dependability                                | 100        |

|     | 5.5                                                                            | Dependable Hardware Architecture                                  |            |

|     | 5.5.1                                                                          | Principle of Workflow                                             |            |

|     | 5.5.2                                                                          | Pros and Cons of Proposed Approach                                |            |

|     | 5.6                                                                            | Simulations and Results                                           |            |

|     | 5.6.1                                                                          | Target System                                                     |            |

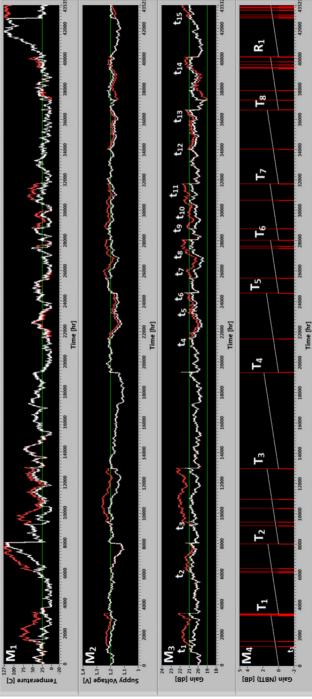

|     | 5.6.2                                                                          | The Simulation Environment                                        |            |

|     | 5.6.3                                                                          | Simulation Results of the Target System.                          |            |

|     | 5.6.4                                                                          | Comparison of the Simulation Results                              |            |

|     | 5.7                                                                            | Conclusions                                                       |            |

|     | 5.8                                                                            |                                                                   |            |

|     | 3.8                                                                            | References                                                        | 110        |

| 6   | Perfe                                                                          | ormance Degradation Analysis and Dependability Enhancement of SAR | ADCs 121   |

|     | 6.1                                                                            | Introduction                                                      | 121        |

|     | 6.2                                                                            | The Charge Redistribution SAR ADC                                 | 123        |

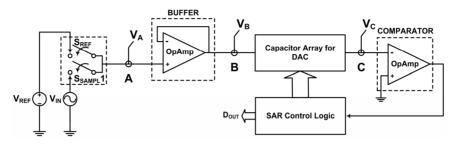

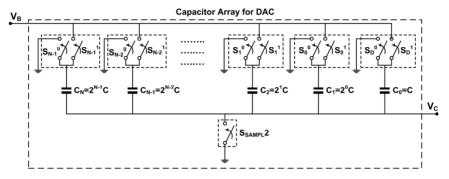

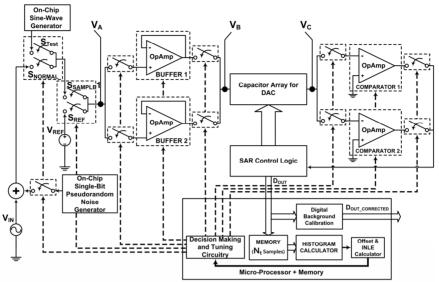

|     | 6.2.1                                                                          | The Working Principle of the ADC                                  | 123        |

|     | 6.2.2                                                                          | Modelling Degradation Effects in the SAR ADC                      | 124        |

|     | 6.2                                                                            | 2.2.1 Modelling the Buffer and Comparator Degradation Effects     | 125        |

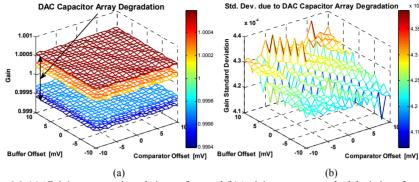

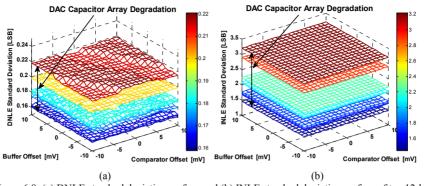

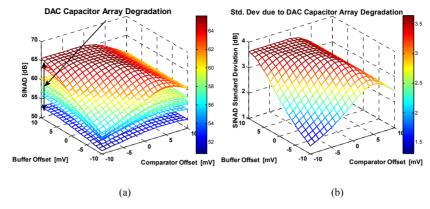

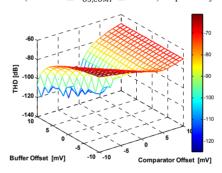

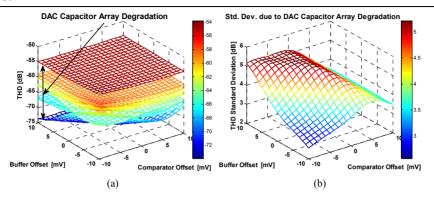

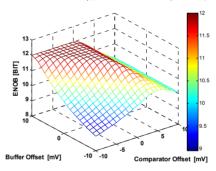

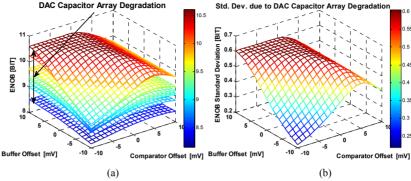

|     | 6.2                                                                            | 2.2.2 Modelling the DAC Capacitor-Array Degradation Effects       | 126        |

|     | 6.3                                                                            | SAR ADC Performance Analysis                                      | 128        |

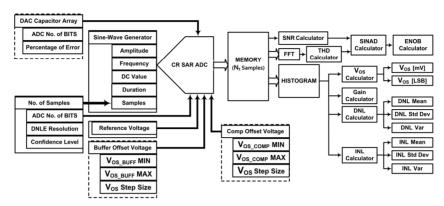

|     | 6.4                                                                            | Simulation Setup                                                  | 130        |

| 6.5 |                                                                                | Simulation Results.                                               | 132        |

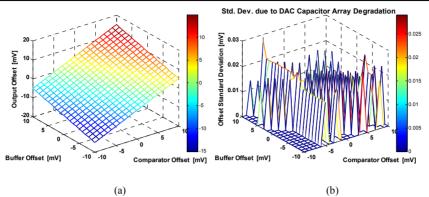

|     | 6.5.1                                                                          | Static Performance Parameter Degradation Results                  | 132        |

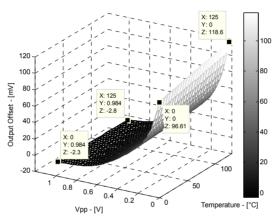

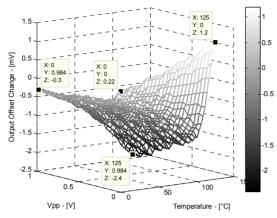

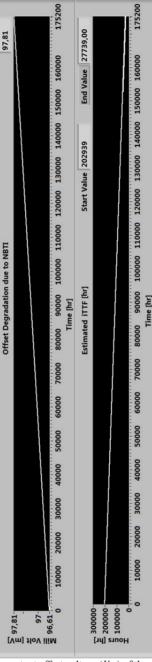

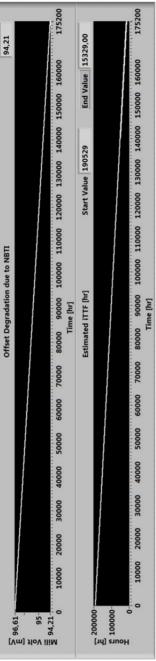

|     | 6.5                                                                            | 5.1.1 The SAR ADC Output Offset Voltage Degradation               | 132        |

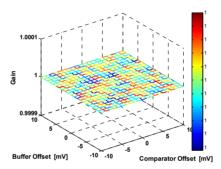

|     | 6.5                                                                            | 5.1.2 The SAR ADC GAIN Degradation                                | 133        |

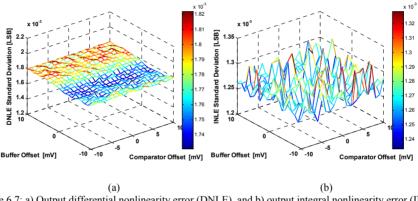

|     | 6.5                                                                            | 5.1.3 The SAR ADC DNLE and INLE Degradation                       | 134        |

|     | 6.5.2                                                                          | Dynamic Performance Parameter Results                             | 135        |

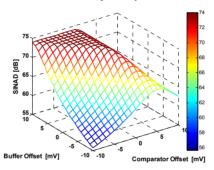

|     | 6.5                                                                            | 5.2.1 SAR ADC SINAD, THD and ENOB Degradation                     | 135        |

|     | 6.5.3                                                                          | Summary of Simulation Results                                     | 138        |

|     | 6.6                                                                            | Potential Critical Performance Parameters                         | 139        |

|     | 6.7                                                                            | Proposed Dependability Enhancement Strategies                     | 140        |

|     | 6.7.1                                                                          | Monitoring Mechanisms                                             | 141        |

|     | 6.7.2                                                                          | Controlling Mechanisms                                            | 141        |

|     | 6.7                                                                            | 7.2.1 Controlling the Buffer and Comparator Offset                | 141        |

|     |                                                                                | B. The Offset Cancellation Technique                              | 141        |

|     |                                                                                | C. Digital Tuning Techniques for Offset                           | 142        |

|     | 6.7                                                                            | 7.2.2 Controlling the DAC Capacitor Array Values                  | 142        |

|     | 6.7.3                                                                          | Dependability Enhancement Strategy                                | 143        |

|     |                                                                                |                                                                   |            |

| 6.7              | 3.1 Dependable Hardware Architecture                                  | 144 |

|------------------|-----------------------------------------------------------------------|-----|

| 6.8              | Conclusions                                                           | 145 |

| 6.9              | References                                                            | 145 |

| 7 Conc           | clusions, Contributions and Future Work                               | 149 |

| 7.1              | Summary of the Research Work                                          | 149 |

| 7.2              | Answers to Research Questions                                         | 152 |

| 7.3              | Conclusions and Main Contributions of our Research Work               | 153 |

| 7.3.1            | The Dependable Hardware Platform                                      | 153 |

| 7.3.2            | The Library of Dependable IPs                                         | 154 |

| 7.3.3            | The Dependable Workload-Sharing Duplication System                    | 154 |

| 7.3.4            | Process-Induced Initial-Value Dependent Workflow                      | 155 |

| 7.3.5            | Direct Runtime Reliability-Estimation Technique                       | 155 |

| 7.3.6            | Indirect Runtime Reliability-Estimation Technique                     | 155 |

| 7.3.7            | Differentiating Between Short-Term and Long-Term Dependability Issues | 156 |

| 7.3.8            | Behavioral Model-Based Degradation Analysis System                    | 156 |

| 7.3.9            | A Flexible Degradation-Analysis System for SAR ADCs                   | 156 |

| 7.4              | Possible Limitations of this Research Work                            | 157 |

| 7.5              | Future Work and Recommendations.                                      | 158 |

| 7.6              | References                                                            | 158 |

| Abbreviations    |                                                                       | 161 |

| List of Publicat | tions                                                                 | 165 |

| Biography        |                                                                       | 167 |

# CHAPTER 1

**INTRODUCTION**

ABSTRACT — This chapter presents an introduction to the research presented in this thesis. The results of technology scaling in CMOS technology on one side have improved performance, power consumption and fabrication costs. On the other hand they have introduced complex dependability issues in electronic system design. These electronic systems, being an indispensable part of our daily life, demand an increasing dependability especially in safety-critical applications. Traditional methods to cope with these dependability issues are not suitable anymore for electronic systems designed in these advanced technology nodes. This requires new methodologies at device, circuit and system levels. The research in this thesis investigates these issues and provides solutions at system-level in order to improve the dependability of analog and mixed-signal circuits and systems on a chip.

CMOS technology has been the dominant integrated circuit (IC) technology for nearly four decades following the trends predicted by Moore's Law. This trend of ongoing technology scaling has resulted in a revolution in electronic industry and the electronic system performance has increased multiple orders in scale. On one side it has allowed us possible to integrate multi-billion of transistors (NViDIA: 7.1 billion in 28 nm) on a single chip [Hal12]. However, on the other hand power, energy, and variability issues have increased. The reduced transistor geometries and the corresponding increase in transistor densities have made it possible to integrate complex systems on a chip. The above trend also includes analog, RF and mixed-signal modules in these chips.

Today, these electronic systems are an indispensable part of our life. They are frequently utilized to support the human activities in civilian, industrial, and military applications. Sometimes their presence is easy to recognize, like in the automatic vending machines, digital clocks, desktop or laptop computers etc. Sometimes their presence may not be easily recognizable, like in an electro-mechanical unit controlling the operations of the engine or brakes of our car. The human dependence on these systems relies on the services delivered by these electronic systems. The quality of services delivered becomes extremely important in case these electronic systems are used in safety-critical applications, where any failure may result in loss of human lives, damage of environment, or loss of money. This reliance in the ability of an electronic system to deliver the agreed services in the specified time is called the dependability of the system. System-level techniques that can be used to enhance this reliance in

delivering agreed services or system dependability of analog and mixed-signal systemson-chip is the main subject of this thesis.

The remainder of the chapter is organized as follows. The dependability of electronic systems and its importance in our daily life is presented in section 1.1. The advances in recent technology scaling have introduced many problems that can degrade the dependability of these electronic systems, which are discussed in section 1.2. Section 1.3 discusses the dependability issues in analog and mixed-signal systems as a result of technology scaling. Furthermore, the possible pitfalls in traditional dependability improvement methodologies are briefly discussed in section 1.4. The research problem tackled in this thesis and the presented approach are summarized in sections 1.5 and 1.6 respectively. Finally, the overall thesis organization and some important references are presented in sections 1.7 and 1.8 respectively.

#### 1.1 DEPENDABILITY AND ITS IMPORTANCE

Dependability on electronic systems has become essential in our modern-day society. It represents the degree of user confidence that the system will operate as expected and that the system will not fail in normal use [Avi01]. In safety-critical systems it is the most important property. If these systems fail to deliver their services then serious problems and significant losses may result. Usually systems where a user cannot trust the normal behavior will be simply rejected. It may lead to further rejection of other products from the same company believing that these products are perhaps untrustworthy as well. In some cases a dependability failure of a sub-system may result in a complete system failure and hence result in enormous cost damage. For example, failure in the control system of a reactor or an aircraft navigation system may result in damage which is orders of magnitude larger than the cost of the control system itself.

In case there is a mechanical problem in an aircraft, then as a requirement of dependability the whole aircraft should not depend on that one component (single point of failure). Therefore, usually these critical systems have backup or redundancy systems built into their designs. For example, aircrafts normally have more than one engine to backup if one engine fails. Therefore, maintaining or achieving high system dependability especially in safety-critical systems is the most important property.

The next section will briefly discuss how the technology scaling has introduced dependability problems in integrated electronic systems.

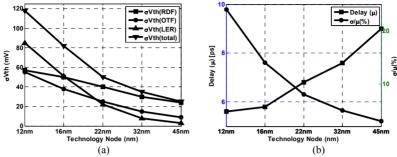

#### 1.2 DEPENDABILITY ISSUES IN ADVANCED TECHNOLOGY NODES

Traditionally, technology scaling has improved electronic circuits in their performance, low energy consumption and lower die cost. However, new technologies are far less mature as compared to older technologies because they require new materials and process steps that have not yet been thoroughly characterized [Mae05]. Moreover, temporal degradations as a result of smaller feature size and interfaces (wires) are increasing due to increasing electrical fields and temperatures [Gro05]. The electrical characteristics of the transistors and the wires will vary statistically in a spatial and a temporal manner, directly translating into design uncertainty during fabrication

2

Η

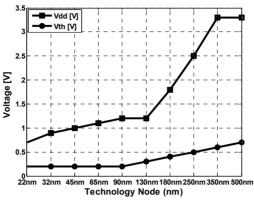

a result, time-dependent uncertainties become a great threat to the design of complex systems-on-chip (SoC) implementations. Characterizing a number of new materials, for example high-k dielectrics, and their interaction with degradation mechanisms is extremely difficult [Miy02, Rib05]. Furthermore, supply voltage scaling has been saturating in order to keep sufficient headroom between the transistor threshold voltage and the supply voltage, hence increasing the electrical fields and stress conditions for these scaled devices. In addition, effects like:

and even during operational life. This combined impact of manufacturing uncertainty (process variability) and temporal degradation results in time-dependent variability. Unfortunately, traditional worst-case design slacks or margins are not sufficient anymore to capture the temporal degradation in circuits and hence systems [Gro05]. As

- soft-breakdown (SBD) in gate oxide of transistors (especially dramatic in high-k oxides) [Gro05],

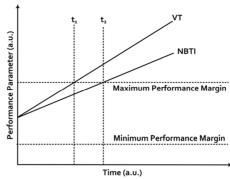

- Negative Bias Temperature Instability (NBTI) issues in the threshold voltage of the PMOS transistors [Red02].

- Hot Carrier Injection (HCI) issues in the drain current of MOSFETs [Bra09].

- Electro-Migration (EM) problems in copper interconnects [Bru05], breakdown of dielectrics in porous low-k materials [Tok05],

are now becoming clear threats for the functional operation of the circuits and systems in near future technologies. The net result is that it becomes increasingly difficult to guarantee the life time and hence the dependability of electronic systems in new technology nodes.

#### 1.3 DEPENDABILITY ISSUES IN ANALOG AND MIXED-SIGNAL SYSTEMS

With the introduction of nano-scale CMOS technologies, analog and mixed designers are faced with many new challenges at different phases of design. These challenges include severe degradation in device matching characteristics as a result of device and lithographic quantum limits [Lew09]. Non-idealities in scaled technologies also have a significant effect on analog and mixed-signal systems, including effects on gain, linearity and noise figure.

Analog and mixed-signal systems, being an important part of most critical systems especially in automotive, medical and military systems have received little attention with regard to dependability. With designs moving towards smaller dimensions, electric fields in the channels are becoming larger, causing more energetic electrons to damage the channel-oxide and hence degrading the circuit performance. The introduction of new surface-channel pMOSFETs for analog circuits, on one side, has made it possible to fabricate both digital and analog circuits on the same chip, while on the other hand, has increased the effects due to NBTI and HCI [Jha05] and hence degradation in the analog and mixed-signal circuit performance. Furthermore, in case of analog circuits, dc biasing voltages always exist irrespective of the input signal. In addition, because of the high-density of digital circuitry present nearby the analog circuitry on the same chip, a high temperature may also exist in addition to the challenges of the applied dc gate and

Α P Т E R

1

drain voltages. This would result in a continuous stress (voltage and temperature) in analog circuits. As many analog circuit operations require matched parameters therefore any mismatches introduced by these continuous stresses will cause performance degradations or circuit failures [Jha05] and can impose a fundamental limit to the analog and mixed-signal circuit dependability.

The next section will briefly discuss the difficulties associated with enhancing the dependability of these analog and mixed-signal systems using *traditional* techniques. This will lead to the formulation of the problem statement for this research thesis.

#### 1.4 TRADITIONAL DEPENDABILITY IMPROVEMENT PITFALLS

In new technology nodes, the traditional worst-case analysis and system design paradigms are breaking down because of the increasing dynamism present in modern applications. The way degradation problems appear within these electronic systems is a quite random process and it depends on the actual operating conditions: time, temperature and stress voltages etc. [Sta01]. This is especially true for large circuits and systems featuring many transistors which can undergo significantly different stress conditions while executing dynamic applications. This fact simply indicates that innovation in electronic design and analysis has to take place to counteract the impact that temporal parametric degradations will have on the actual useful life-time of electronic systems.

Traditional worst-case analysis, where designers tune their electronic designs to meet the performance constraints for all the corner-points, is still widely used in industry. However, it suffers from a number of disadvantages. Selected corner points are usually very pessimistic because it is extremely unlikely that all the parameters will have their maximum or minimum values simultaneously. Therefore, the design margins required to make the analog and mixed-signal systems operational under all corner conditions are excessive. Furthermore, the number of parameters affected by timedependent variability becomes very large (e.g. ADC static and dynamic parameters as explained in Chapter 6). This means that analog and mixed-signal system designers will have to deal with parameter spaces of many dimensions and an extremely large number of corner points. Finally, worst-case analysis techniques cannot handle the impact of intra-die time-dependent variability, which is spatially uncorrelated in nature [Naj05]. This is because the electrical parameters of each transistor would become an additional axis in the parameter space and the complexity would become unmanageable. This means the worst-case margin added by system designers on top of the worst-case circuit tuning already performed by circuit designers will result in increasingly larger safety margins. In short, with design-time tuning of the electronic systems it will be very difficult to meet the performance constraints during the operational life. This leads to exploring and investigating new solutions which are the subject of this research thesis as formulated in the next section.

Being the interface between the real world and the digital world, analog and mixedsignal front/back ends are an essential part of most safety-critical systems. The goal of this research is to explore and investigate new techniques that can potentially be used to enhance the dependability of these analog and mixed-signal front ends despite the unsuitable traditional worst-case design techniques. As discussed above, on one side the technology scaling has improved electronic circuits in their performance, low energy consumption and lower die cost. While on the other hand, it has introduced new special, temporal and dynamic variations. The focus of our research will be on temporal variations that can result in temporal degradation of electronic system performance and hence a potential cause of dependability degradation. Among the different parts of an analog and mixed-signal front end only the amplifiers and analog-to-digital converters (ADCs), being relatively generic to every analog and mixed-signal front end, are considered for dependability investigations. The sensor/actuator part being relatively different for every application and quite often related to micro-electro-mechanicalsystems (MEMS) has not been considered for dependability improvements. exclusion of sensor/actuator parts will have no influence on the proposed dependability enhancement techniques presented in this thesis.

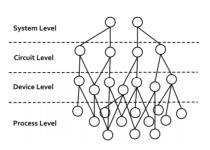

Different levels of investigation and improvement can be considered for the amplifier and ADC part, namely device level, circuit level, and system level. However, our research will consider only system-level techniques. The amplifier and ADC being considered in continuous and discrete time (digital) domains come with a handful of performance parameters. As will be shown later in this thesis, potentially most of these performance parameters of the amplifier and ADC will be affected by temporal variations. This will make the whole problem complex and unmanageable. However, our goal is to find and investigate only critical and important performance parameters that are usually application dependent. As discussed above, solutions to static variations already exist and are usually practiced at the design stage. However, the combined impact of manufacturing uncertainty (process variability) and temporal degradation (aging) results in time-dependent variability requires a new approach in system design solutions. In reality, as a result of time-dependent variations, the performance parameters of each system component will follow a statistical distribution. Some components will have the value of performance parameters higher than the mean value and some will have a lower value. This variation is usually not exploited in traditional techniques dealing with variations at the system level. New techniques are required in the design of the analog and mixed-signal systems-on-chip at system level to overcome these limitations. This means, using design-time tuning of the electronic systems it will be difficult to meet the performance constraints during the operational life. Therefore, the goal of our research is to exploit system-level techniques that can potentially be used during the operational life of electronic systems to enhance their dependability. The research goal of this thesis can be arranged in a number of questions as follows:

1) What type of hardware architecture can be used to address the technologyscaling related temporal-degradation (aging) issues in analog and mixedsignal (AMS) systems during their operational life? **5**

C H A P T E R

- 2) How can optimization be achieved among different dependability requirements and other issues like area, power, speed etc. in AMS systems?

- 3) What type of improvements will be necessary in the hardware architecture to address the initial-value dependent degradation issues in AMS systems?

- 4) What type of efficient methodologies can be used in order to indirectly estimate the performance of AMS systems during their operational life?

- 5) What (additional) actions will be required to distinguish between timedependent variations and dynamic variations (i.e. long-term and short-term variations as explained in Chapter 5) in order to enhance the dependability of AMS systems?

- 6) What type of alternative methods, as compared to conventional devicelevel simulations, can be used to analyze/investigate time-dependent variations/degradations in complex analog and mixed-signal systems (e.g. analog-to-digital converters)?

The details of the corresponding answers to these research questions are analyzed and concluded in Chapter 7. The next section will summarize the presented approach to address the above research questions.

#### 1.6 PRESENTED APPROACH

The approach presented in this thesis is mainly theoretical and is based upon mathematical models or workflows developed during this research. However, a number of transistor-level simulations are carried out in order to extract the degradation information that is further used at system-level to analyze and investigate presented dependability improvement strategies.

Initially, a hardware platform is proposed to address temporal-degradation issues in AMS systems in order to enhance the dependability. This hardware platform is further modified to address area overhead and other complexity issues. The dependability improvement of both of the proposed hardware platforms is then analyzed mathematically and compared against traditional approaches.

In the next step, process-induced initial-value dependent degradation information is utilized to propose a workflow for better management of system dependability during operational life. Direct and indirect means of extracting system performance (later used to estimate the system reliability) during operational life are also included in this workflow. The proposed approach is mathematically developed and then simulated for a target system under a number of scenarios.

Short-term and long-term environmental changes may lead to corresponding short-term (dynamic) and long-term (time-dependent) dependability issues. Therefore, in order to separate dynamic (short-term) variations from time-dependent (long-term) variations another workflow is presented, analyzed and later simulated for a target system under a number of environmental conditions. To simplify degradation analysis for complex analog and mixed-signal systems a behavioral model based approach is also presented and simulated for a charge-redistribution successive approximation register (SAR) ADC.

In short, a number of methods in order to better analyze the dependability issues in AMS systems and corresponding dependability improvement strategies under time-

dependent, initial-value dependent, and environment dependent degradation issues are presented. Furthermore, an optimization technique to overcome area overhead and corresponding compromises in power, speed, and dependability requirements is also presented.

The next section will briefly discuss the overall organization of the presented approach in this thesis.

#### 1.7 THESIS ORGANIZATION

The thesis is organized as follows. The necessary background information required for this research work including state-of-the-art, their shortcomings and potential considerations in the current research work are briefly described in Chapter 2.

The system-level dependability issues of a general purpose analog and mixed-signal front end and the corresponding dependability improvement hardware architecture are proposed and analyzed in Chapter 3. In addition, further improvements in the proposed dependability improvement hardware architecture to overcome area overhead are also presented in this chapter. An optimization technique, based on a library of dependable IPs (intellectual property) to select the best possible system modules (IPs) under required dependability levels, and area, power, speed issues is also the subject of Chapter 3.

Issues related to initial-value dependent degradations, their consequences on system performance and further improvements in the proposed hardware platform to address these issues are presented in Chapter 4. To overcome complexity and loading issues in monitoring system performance due to temporal degradation has also been resolved in Chapter 4. This is accomplished by providing a novel technique for indirectly estimating the system performance using a set of degradation values over input stress conditions acquired via design-time simulations.

The influence of dynamic (short-term) and temporal (long-term) variations, the method to differentiate between these two types of variations and potential benefits in improving the overall dependability of analog and mixed-signal systems are presented and discussed in Chapter 5.

In order to resolve degradation analysis issues in complex analog and mixed signal systems, a system-level degradation analysis system for a charge-redistribution SAR ADC is presented in Chapter 6. It is based on incorporating circuit-level degradation information in system-level behavioral models.

In Chapter 7, the overall contribution of the research presented in this thesis is summarized and possible limitations of the proposed methodology and potential future work in improving the dependability of analog and mixed-signal front ends are discussed.

#### 1.8 REFERENCES

[Avi01] A. Avizienis, J-C. Laprie, and B. Randell, "Fundamental concepts of dependability", in Laboratory for Analysis and Architecture of Systems (LAAS-CNRS) Technical Report no. 01-145, Apr. 2001.

[Bra09] A. Bravaix, et al., "Hot-Carrier acceleration factors for low power management in DC-AC stressed 40nm NMOS node at high temperature," in IEEE Int. Reliability Physics Symposium, pp. 531-548, 2009.

[Bru05] C. Bruynseraede, et al., "The impact of scaling on interconnect reliability," in IEEE Int. Reliability Physics Symposium, pp. 7-17, 2005.

[Gro05] G. Groeseneken, R. Degraeve, B. Kaczer, and P. Roussel, "Recent trends in reliability assessment of advanced CMOS technologies," in IEEE Int. Conf. Microelectronic Test Structures (ICMTS), pp. 81-88, 2005.

[Hall2] G. Halfacree, "Nvidia announces world's most complex GPU," in bit-tect news, 2012. http://www.bit-tech.net/news/hardware/2012/05/18/nvidia-gk110/1

[Jha05] N.K. Jha, P.S. Reddy, D.K. Sharma, and V.R. Rao, "NBTI degradation and its impact for analog circuit reliability," in IEEE Trans. Electron Devices, Vol. 52, No. 12, pp. 2609-2615, 2005

[Lew09] L.L. Lewyn, T. Ytterdal, C. Wulff, and K. Martin, "Analog Circuit Design in Nanoscale CMOS Technologies," in IEEE Proceedings, Vol. 97, No. 10, pp. 1687-1714, 2009.

[Mae05] K. Maex, et al., "Technology aware design and design aware technology," in IEEE Int. Conf. Integrated Circuit Design and Technology (ICICDT), pp. 77-81, 2005.

[Miy02] S. Miyazaki, "Characterization of high-k gate dielectric/silicon interfaces," in Applied Surface Science, Vol. 190, Issues 1–4, pp. 66-74, 2002.

[Naj05] F.N. Najm, "On the need for statistical timing analysis," in IEEE Design Automation Conference (DAC), pp. 764-765, 2005.

[Red02] V. Reddy, et al., "Impact of negative bias temperature instability on digital circuit reliability," In IEEE Reliability Physics Symposium, pp. 248-254, 2002.

[Rib05] G. Ribes, et al., "Review on High-k Dielectrics Reliability Issues" in IEEE Trans. Device and Materials Reliability, Vol. 5, No. 1, pp. 5-19, 2005.

[Sta01] J.H. Stathis, "Physical and predictive models of ultrathin oxide reliability in CMOS devices and circuits," in IEEE Trans. Device and Materials Reliability, Vol. 1, No. 1, pp. 43-59, 2001.

[Tok05] Z. Tokei, Y. Li, and G. Beyer, "Reliability challenges for copper low-k dielectrics and copper diffusion barriers," in Journal of Microelectronics Reliability, pp. 1436–1442, 2005.

### BACKGROUND AND RELATED WORK

ABSTRACT — This chapter presents the necessary background knowledge essential to understand the achievements in this research work. It starts with the concept and definition of dependability. Next it's most important attributes (reliability, maintainability, and availability) as well as the sources of impairments and the means to improve dependability are presented. Mathematical theory necessary to understand these dependability attributes is also explained. Physical mechanisms responsible for causing failures and degradations are also briefly discussed. At the end, a brief overview of previous research, their limitations and shortcomings as well as a summary of important issues addressed in this thesis in order to enhance the dependability of analog and mixed-signal systems at system level are described.

#### 2.1 Introduction

The rapid advances in microelectronic, computer and networking systems have resulted in their penetration into almost every aspect of our life. They are utilized to support the human activities and as a result these activities depend more and more on the services delivered by these systems. As the technology is scaling rapidly, the complexity of these systems is also getting higher and higher. Therefore, the chance of a fault that impedes the delivery of the service has become greater than ever. As a result, failure of these systems could result in a loss of time, money, damage to environment, or even human life in some critical applications. Therefore, the assessment and improvement of system dependability becomes a key step in the design, analysis, and tuning of such systems.

The rest of the chapter is organized as follows. The definition of dependability, its attributes and the possible dependability impairments and means are presented in section 2.2. Among different attributes of dependability a number of attributes have been selected for the research work presented in this thesis. These attributes and their theory are being discussed in sections 2.3 and 2.4 respectively. Section 2.5 briefly describes different failure mechanisms that can be responsible for dependability degradation. A brief overview of best-practice methods, their limitations along with important considerations being addressed in this current research work in order to enhance the dependability of analog/mixed-signal systems are discussed in section 2.6. The conclusions and some important references are presented in sections 2.7 and 2.8 respectively.

#### 2.2 DEPENDABILITY

The term dependability is reported to have been first used as a technical term in 1960 by Hosford [Pra95]. Its early usage was confined to the notions of availability and reliability. In the meantime, J.C. Laprie expanded the term dependability as a wider concept in 1985 [Lap85] because the meaning of "reliability" that the fault-tolerance technology treated had broadened. From then on, dependability has been used in various fields to this day.

Unfortunately, the term dependability has been assigned many different meanings in the literature. For example, in the case of computer-based systems, dependability has been defined as [Par88]:

"the justifiable confidence the manufacturer has that it will perform specified actions or deliver specified results in a trustworthy and timely manner"

Avizienis et al. defined the dependability of a system as [Avi04]:

"the ability to deliver service that can be justifiably trusted"

Where the service delivered by a system is its behavior as it is perceived by its user(s); a user is another system (human or physical) which interacts with the former. However, according to the classical definition of dependability it represents the property of the system that integrates attributes, like availability, reliability, maintainability, safety, integrity and confidentiality [Avi01, Avi04, Buj06]. Usually, dependability is classified into three fundamental characteristics: attributes, impairments and means. The dependability *attributes* are the system properties that are expected from a system. The dependability *impairments* represent the potential threats to dependability and the dependability *means* are the methods or techniques that can be used to build a dependable system. These characteristics are further discussed in the next sections.

#### 2.2.1 DEPENDABILITY ATTRIBUTES

The attributes of dependability are the system properties that can be expected as a requirement of its service to be delivered. There are a number of system properties that can be considered as the dependability attributes like reliability, availability, maintainability, safety, integrity and confidentiality [Avi01]. Depending on the application, one or more of these attributes may be needed to appropriately evaluate system behavior. For example, for a nuclear power plant system the reliability and safety will be the most important attributes.

The different attributes of dependability can be defined as [Avi01]:

**Availability:** This indicates the readiness of a system for its correct service. It is defined as the probability that a system will be available to correctly deliver its service at any given time.

**Reliability:** This shows the capability of a system to provide the continuity of its correct service. It is defined as the probability that a system will be

**Maintainability:** This indicates the capability of a system to undergo modifications and repairs. It is defined as the probability that a system will be repaired at any given time if it fails to deliver correct functionality.

**Safety:** This is defined as the capability of the system to avoid catastrophic consequences on the users or the environment.

**Integrity:** This is the capability of a system to avoid any alterations. It can be further classified in to two types:

- **1. System integrity** which defines the ability of a system to detect faults in its own operations and to inform a human operator.

- **2. Data integrity** which defines the ability of a system to prevent damage to its own database and to detect, and possibly correct, errors that occur as a consequence of faults.

**Confidentiality:** This is the capability of a system to prevent the unauthorized disclosure of information.

Among the above attributes of dependability, only the first three namely the availability, reliability and maintainability will be considered in the research work presented in this thesis as discussed in section 2.3.

#### 2.2.2 DEPENDABILITY IMPAIRMENTS

The impairments of dependability are the reasons that could prevent a system from correct functioning [Avi01]. Usually, they are described in terms of faults and failures. A system failure is an event that occurs when the delivered service deviates from the correct service. A failure is thus a transition from the correct service to the incorrect service, i.e. not implementing the system function. Faults are the basic cause that can lead to failures in the system. Faults can occur as a result of numerous problems at the specification, implementation or fabrication level. These could be external factors as well; including environmental disturbances or human actions, either accidental or deliberate

#### 2.2.3 DEPENDABILITY MEANS

The means of dependability are the methods and techniques that facilitate the development of dependable systems [Avi01]. Usually, they are classified into four types. Fault prevention is the method that is used to prevent the occurrence or introduction of faults. For example, shielding and radiation hardening to prevent radiation-induced faults and training and maintenance to prevent user-induced faults. Fault tolerance is the method that is used to develop a system so that they function correctly in the presence of faults. Usually, fault tolerance is achieved by using some sort of redundancy. Fault removal is the method that is used to reduce the number of faults which are present in the system. It is normally achieved by verification, diagnosis, and correction procedures performed during the system development phase or by

11

C

H A P T E R

2

corrective and preventive maintenance procedures performed during the system operational life. *Fault forecasting* is the method that is used to estimate current faults, possible future fault occurrences and the consequences of faults. It is normally performed by evaluating the system behavior with respect to fault occurrences either qualitatively, quantitatively or probabilistically.

## 12

#### 2.3 SELECTED DEPENDABILITY ATTRIBUTES

As described in Chapter 1, the aim of this research is to explore and investigate new techniques that can be used to enhance the dependability of analog and mixed-signal front ends. However, as described above, the dependability of a system based on its application is a collection of system properties like availability, reliability, maintainability, safety, integrity and confidentiality which are expected from a system. Therefore, one or more of these properties will be required to appropriately evaluate the dependability of analog and mixed-signal front ends. Being an important part of most critical systems, the dependability of analog and mixed-signal systems requires that they should always be available for functionally correct service and be maintained/repaired as quick as possible. Therefore, among different attributes of dependability the reliability, maintainability, and availability will be the focus of current research presented in this thesis.

#### 2.4 DEPENDABILITY THEORY

In this section, the necessary mathematical theory behind the reliability, availability and maintainability will be discussed. These theories are stated in terms of the mathematics of probability and statistics because of the inherent degree of uncertainty in predicting a failure and associated repair actions. Hence the uncertainties of failures or repairs are given in percentages or probability that a given part will fail or can be repaired in a specified time.

#### 2.4.1 RELIABILITY THEORY

As mentioned in section 2.1, the reliability can be defined in terms of probability as "the probability that a system will be available to correctly deliver its service at any given time", mostly under predefined conditions. The general expression for the reliability function is given by [Kan11]:

$$R(t) = e^{-\lambda t} \tag{2.1}$$

where ' $\lambda$ ' represents the constant failure rate which is defined as the number of failures per unit time. Equation 2.1 is frequently used in reliability analysis, particularly for electronic systems. This is also known as the *exponential failure law* [Kan11].

Several other commonly-used reliability concepts involve mean-time-between-failures (*MTBF*) and mean-time-to-failure (*MTTF*). Usually *MTBF* is the predicted elapsed time between inherent failures of a system during operation [Eus08, Wik14a].

2

13

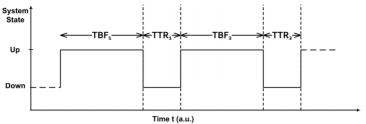

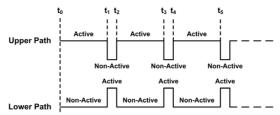

Figure 2.1: Time-between-failures (TBF) and time-to-repair (TTR) for a repairable system.

This is the expected value of the arithmetic mean (average) time between failures of a system. This concept is typically defined for repairable systems (finite repair time) where a failed system is repaired as a part of a renewal process. However, *MTTF* is typically defined for non-repairable systems (infinite repair time) and this represents the expected value of the average time to failure of a system [Eus08, Wik14a].

Figure 2.1 shows the "Up" and "Down" state of a repairable system. The time spent in "Up" state between the two consecutive "Down" states is defined as the time-between-failures (*TBF*). Therefore, mathematically for repairable systems the *MTBF* can be defined as:

$$MTBF = \frac{\sum_{i=1}^{n} TBF_i}{n} \tag{2.2}$$

where

$$\sum_{i=1}^{n} TBF_i = \text{total operating (up)time and}$$

$$n = \text{total number of failures}$$

This means 1/MTBF represents the total number of failures per unit time or as previously defined the failure rate ( $\lambda$ ). Therefore, equation 2.1 in the case of constant failure rate can be rewritten as:

$$R(t) = e^{-t/MTBF} (2.3)$$

This is another well-known equation used in reliability world. This equation gives the reliability of the system in terms of probability; '1' being the highest probability (highly reliable) and '0' being the lowest probability (highly unreliable). An important conclusion that can be drawn from this equation is that at any time 't' the reliability R(t) of the system is directly related to the MTBF value. The larger the value of MTBF is the higher the reliability R(t) of the system will be and vice versa.

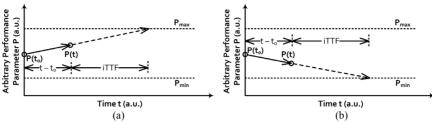

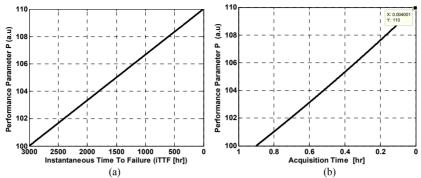

Furthermore, if 'iTTF(t)' represents the instantaneous-time-to-failure, defined as the remaining time before the failure occurs at any time 't', as shown in Figure 2.2 then the reliability of a repairable system at that time can be approximated by:

$$R(t) \cong iTTF(t) \tag{2.4}$$

This equation gives the *quantitative* value of the reliability for a repairable system MTBF and 'zero' being the highest and lowest reliability values respectively. In other

Figure 2.2: Instantaneous-time-to-failure (iTTF(t)) for a repairable system.

words, the larger the value of time before the system failure occurs the higher the reliability of the repairable system will be and vice versa. Equation 2.4 is further used in Chapter 4 to calculate the reliability of a repairable system during its operational life.

#### 2.4.2 MAINTAINABILITY THEORY

The main purpose of the maintainability is to design a system such that it can be repaired if a failure occurs. As mentioned in section 2.1, the maintainability can be defined in terms of probability as "the probability that a system will be repaired at any given time if it fails to deliver the correct functionality". Mathematically it is usually expressed as [Rel14b]:

$$M(t) = 1 - e^{-\mu t} (2.5)$$

where ' $\mu$ ' represents the constant repair rate which is defined as the number of repairs per unit time. The concept of maintainability is typically defined for repairable systems and is usually related to mean-time-to-repairs (MTTR). Where MTTR is usually defined as the expected value of the mean (average) time required to repair a failure in a repairable system [Eus08, Wik14b]. Figure 2.1 shows the time-to-repair ( $TTR_i$ ), defined as the time required to repair a system when  $i^{th}$  failure occurs, for a repairable system. Therefore, mathematically the MTTR can be defined as:

$$MTTR = \frac{\sum_{i=1}^{m} TTR_i}{m} \tag{2.6}$$

where

$$\sum_{i=1}^{m} TTR_i = \text{total repair (down)time and}$$

$$m = \text{total number of repairs}$$

This means 1/MTTR represents the total number of repairs per unit time or as previously defined the repair rate ( $\mu$ ). Therefore, equation 2.5 in the case of constant repair rate can be rewritten as:

$$M(t) = 1 - e^{-t/MTTR} (2.7)$$

This is the general expression for the maintainability function. This equation gives the maintainability of a repairable system in terms of probability; '1' being the highest

(14)

probability (highly maintainable) and '0' being the lowest probability (highly unmaintainable).

#### 2.4.3 AVAILABILITY THEORY

Similar to maintainability, the availability concept is usually used for repairable systems that are required to operate continuously, i.e., round the clock. A system, at any random point in time, can be either operating (up) or "down" because of a failure as shown in Figure 2.1. Therefore, in this original concept a repairable system is considered to be in only two possible states - operating or in repair. In this way, the availability is defined as the probability that a system is operating satisfactorily at any random point in time 't', when subject to a sequence of "up" and "down" cycles (Figure 2.1). Mathematically, availability can be expressed as:

$$A = 1 - \frac{Down \, Time}{Total \, Time} = \frac{Up \, Time}{Total \, Time} = \frac{Up \, Time}{Up \, Time + Down \, Time}$$

(2.8)

Using equations 2.2 and 2.6, equation 2.8 can be rewritten as:

$$A = \frac{n \times MTBF}{n \times MTBF + m \times MTTR} \tag{2.9}$$

In the case, the total number of failures 'n' and total number of repairs 'm' are equal then the above equation reduces to:

$$A = \frac{MTBF}{MTBF + MTTR} \tag{2.10}$$

This means, availability is a combination of reliability (MTBF) and maintainability (MTTR) parameters. This equation is the general expression for the availability function which is frequently used in literature. Furthermore, by incorporating the concept of instantaneous-time-to-failure (*iTTF*), as defined above, the availability of a repairable system at any time 't' during its operational life can be approximated by:

$$A(t) \cong \frac{iTTF(t)}{iTTF(t) + MTTR} \tag{2.11}$$

This equation is further used in Chapter 4 to calculate the availability of a repairable system during its operational life.

#### 2.5 DEGRADATION MECHANISMS AND SYSTEM DEPENDABILITY

As a result of continuous aggressive scaling of technology in terms of device dimensions, increasing electric fields and the usage of new materials to meet the demands set by these technologies, the reliance on electronic systems fabricated in these technology nodes has become a very important aspect. There are various degradation

15

C H A P T E R

2

mechanisms that can degrade the performance of devices, circuits and their associated electronic systems as a result of this aggressive technology scaling. In this section some of the important degradation mechanism that include bias temperature instability (BTI), hot carrier injection (HCI), time dependent dielectric breakdown (TDDB), and electromigration (EM) are briefly introduced.

## 16

#### 2.5.1 BIAS TEMPERATURE INSTABILITY

The bias temperature instability (BTI) is a degradation mechanism that occurs in MOS devices as a result of interface traps between the gate oxide and silicon substrate at elevated temperatures ( $30^{\circ}C$  to  $200^{\circ}C$ ) [Str09] and hence degrade the dependability of electronic devices. This degradation mechanism results in device threshold voltage ( $V_{th}$ ) shift and loss of drive current ( $I_{on}$ ). The BTI effect is more severe for pMOSFETs than nMOSFETs due to the presence of holes in the PMOS inversion layer that are known to interact with the oxide states. The highest impact of BTI in pMOSFETs is observed if stressed with a high negative gate voltage at elevated temperatures [Ent07]. It is referred to as negative BTI (NBTI) due to the negative gate to source voltage. In pMOSFETs, the channel holes interact with passivated hydrogen bonds in the dielectric resulting into generation of traps and interface states. This results in an increase in threshold voltage ( $V_{th}$ ) value and the effect increases at high temperatures. The introduction of new dielectric material like high-k has increased the BTI effect in nMOSFETs and this is referred to as positive bias temperature instability (PBTI) due to the positive gate-to-source voltage.

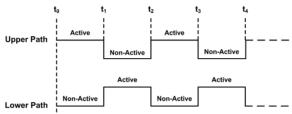

It has been noticed that BTI degradation starts decreasing very quickly after the removal of the stress. This recovery process is caused by de-trapping of charge during subsequent removal of stress signal after a stress phase [Gra07]. The stress signal causing BTI degradation can be of two types; the static stress (DC stress) and the dynamic stress (AC stress). The AC stress is known to be beneficial for lifetime enhancement because it can introduce the recovery process mentioned above [Nig06, Che03, Aba03]. Recovery after NBTI or PBTI stress in MOSFETs and its dependence on gate voltage, temperature and frequency of stress signal has been a hot topic of research in the past decade [Rei10]. Currently, BTI is one of the most serious and important reliability concerns for both digital and analog/mixed-signal CMOS circuits. At advanced technology nodes this effect is enhanced due to reduced voltage headroom, high oxide electric fields resulting from non-constant field scaling, high temperatures due to higher power dissipation and introduction of new dielectric materials.

#### 2.5.2 HOT CARRIER INJECTION

Hot carrier injection (HCI) degradation has been as an important failure mechanism for the last three decades and still remains important in new technologies. HCI occurs when an "electron" or "hole" gains sufficient kinetic energy to overcome a potential barrier and breaks the interface state in MOS devices. These charge carriers can become trapped in the gate dielectric and hence permanently change the transistor characteristics [Mar13, Wik14c]. Therefore, HCI will degrade the electrical characteristics of MOSFETs and hence the dependability of associated electronic systems.

Time-dependent dielectric breakdown (TDDB) is a degradation phenomenon that occurs in the thin insulating layer  $SiO_2$  between the control "gate" and the conducting "channel" of the transistor. The general belief is that TDDB of gate insulating material results from the cumulative effect of insulator trapped charge buildup during short-term and long-term high-field stress. High trapped-charge-induced local fields build up within the insulator which creates defects in the oxide film. These defects accumulate with time and eventually reach a critical density, triggering a sudden loss of dielectric properties [Sta01]. These defects can also cause gate leakage and excess noise in MOSFETs. A surge of current produces a large localized rise in temperature, leading to permanent structural damage in the  $SiO_2$ . This will create failures in MOSFETs and hence the dependability of associated electronic systems will degrade.

#### 2.5.4 ELECTRO-MIGRATION

Electro-migration (EM) is the dominant failure mode of interconnects that results from aggressive interconnect scaling. As the technology is scaling, the device density is increasing and as a result the interconnects that carry signals are consequently reduced in size, specifically, in height and cross section. This leads to extremely high current densities, in the order of at least 106 A/cm2 and associated thermal effects, which can cause reliability and hence dependability problems [Sco91].

#### 2.6 ANALOG AND MIXED SIGNAL DEPENDABILITY IMPROVEMENTS

With the introduction of nano-scale CMOS technologies different degradation mechanisms, as described above, can have a big impact on the lifetime of electronic systems; this is especially true in safety-critical systems running under harsh environments for a long time. Usually these degradation mechanisms have negligible effects on consumer devices (like mobile phones) running under normal environmental conditions. Therefore in these technology nodes, the designers of analog and mixed-signal systems, running under harsh environmental conditions, are faced with many new challenges at different phases of the design.

This section sheds light on some of the previous work that has been done in order to improve the dependability (mostly only reliability) of analog and mixed signal systems. Section 2.6.1 gives the briefly history of different degradation mechanisms. Different efforts made at device level, design level and simulation-tool level along with some of the examples from recent practices to analyze and mitigate these degradation effects are given in section 2.6.2. The corresponding shortcomings and limitations of these practices along with some of the important issues addressed in this research work are presented in section 2.6.3.

## 2.6.1 Brief History

Different degradation mechanisms like NBTI, HCI, TDDB, and EM were first discovered by device scientists in the seventies and eighties. At that time most of the

17